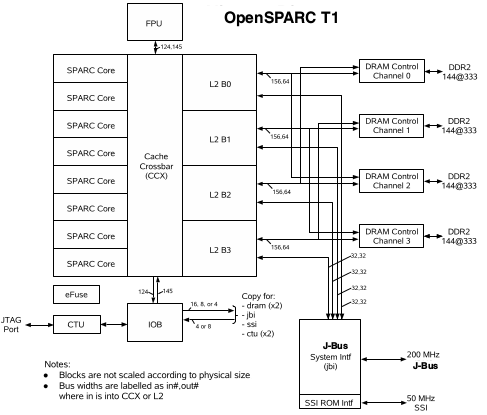

OpenSPARCはオープンソース(GPLライセンス)で公開されているプロセッサの設計データです。OpenSPARCの設計データは、2010年にオラクルに吸収合併されたサン・マイクロシステムズによって公開されました。プロセッサではパソコンなどに搭載されているインテル社の製品が有名ですが、このような商用プロセッサの設計データは通常見ることができません。OpenSPARCは、公開されている商用プロセッサの設計データとして貴重な存在です。現在、OpenSPARC T1と呼ばれるプロセッサと、OpenSPARC T2と呼ばれるプロセッサのデータが公開されています。設計データが公開されたのは、T1が2006年、T2が2008年です。

OpenSPARC T1の設計データの中身

OpenSPARCの設計データには

・RTLデータ(設計ソースコード)

・ドキュメント

・検証環境

・論理合成環境

などが含まれています。

これらのデータを見ると、OpenSPARCの開発について次のことがわかります。

1.どのようにしてプロセッサの検証が行われたか

2.使用されているEDAツール

3.RTLの記述スタイル

1. どのようにしてプロセッサの検証が行われたか

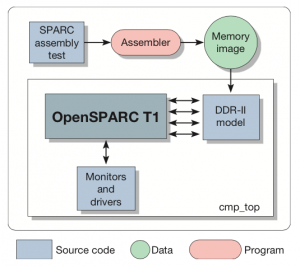

設計データに含まれているドキュメントから、プロセッサの検証フローがわかります。検証フローは、手法としては典型的なものでした。具体的には、

・プロセッサの動作検証用のアセンブラコードからマシンコードを生成

・マシンコードをプロセッサの外部メモリであるDDR-IIに格納

・OpenSPARCでマシンコードを実行

・期待した動作を行うかどうか確認

というフローを、事前に準備したアセンブラコードの数だけ実行しています。

Verilogの標準機能で不足する部分については、C/C++言語で記述した関数をPLI(Programming Language Interface)で登録しています。これらの関数は、主に内部バスのモニターや内部メモリのアクセスに利用されているようです。

2.使用されているEDAツール

OpenSPARC公開当時のLSIの開発で一般的なツールが使用されていました。

| ツール | 製品名 |

|---|---|

| シミュレータ | Cadence社 ncverilog |

| Synopsys社 vcs | |

| 機能検証言語 | VERA |

| デバッグツール | Novas社(当時) Debussy |

3.RTLの記述スタイル

RTLは、完全にハンドメイドのようです。

- フリップフロップはalways文による記述ではなく、個別モジュールとしてインスタンス化するスタイルが多用されている

- 浮動小数点の演算器はゲートレベルに近い、かなり抽象度の低い形で記述されている

DDR I/FやPLIといったプロセッサをの動作を支える周辺機能についてもソースコードがすべて公開されています。通常、これらの周辺機能は、サードパーティ製のIPコアを購入して組み込むことが多く、ソースコードも暗号化されていたりしますが、これらのソースコードも完全に公開されています。

OpenSPARCプロジェクトを動かしてみる

プロジェクトが公開されたのが2006年なので、現在(2015年)動作させようとすると、次のような理由で予想以上に大変な作業でした。

前提としているプラットフォームが古い

OpenSPARCの開発環境は、アセンブルコードのコンパイルなどにPerlを多用しているのですが、前提としているPerlのバージョンが古く、現在の環境では動作しません。

そのまま動かそうとすると、開発環境に含まれているシェアド・ライブラリとの不整合でエラーが発生します。では、その当時の古いバージョンのPerlを入れようとすると、こちらも古すぎて現在のLinux(例えばUbuntu14.04LTS)では簡単にはコンパイルできません。

結局、最新バージョンのPerl+αで動作させることができましたが、試行錯誤にかなりの時間がかかりました。

PLI

C/C++関数で作成したPLI関数をVerilogシミュレータに追加するには、ソースコードをコンパイルする必要がありますが、コンパイルも簡単には通りませんでした。gccなど、開発ツールのバージョンが上がり、OpenSPARC公開当初と比べて微妙に仕様が変わっているためだと思われます。このため、PLI用C/C++ソースコードにはかなり修正が必要でした。

前提としているツールが高価

OpenSPARCの動作をシミュレーションで確認しようとすると、Verilogシミュレータが必要になりますが、設計環境が標準でサポートしているのはncverilogとvcsです。これらのツールは大規模なLSI開発では標準的なものですが、一般ユーザーが購入できるほど安価ではありません。今回はFPGAメーカーの開発ツールに含まれている無償バージョンのシミュレータを利用しましたが、シミュレーション環境の移植にかなり時間がかかりました。

シミュレータの動作例

なんとかFPGA用のModelSimでシミュレーションできるところまでは確認できました。

run -all # Info: reading mem.image # Warning: phyical address out of range(fff0000000) # Warning: phyical address out of range(fff0010000) # Info:zero_bytes address(1000000) bytes(32) dram_begin(40000) dram_end(40002) # Info:zero_bytes address(1000040) bytes(352) dram_begin(40000) dram_end(40006) # Info:zero_bytes address(10001c0) bytes(1856) dram_begin(40004) dram_end(40024) #dram_end(180100) # jbus_clk divider = 12 # dram_clk divider = 14 # cmp_clk divider = 2 # cmp_clk period = 833 # pll_clk frequency = 2400 # Info: Selected Core Clock Frequency 1200 MHz # 20: finish_mask 00000001 # 20: good_trap list 0000082000:1000122000:1130000118 # 20: good_trap 0000082000 # 20: good_trap 1000122000 # 20: good_trap 1130000118 # 20: bad_trap list 0000082020:1000122020:1130000128 # 20: bad_trap 0000082020 # 20: bad_trap 1000122020 # 20: bad_trap 1130000128 # Time: 100 ps Iteration: 0 Instance: /cmp_top/slam_init/l2warm # Info Core_status(1) number(1) # 20000: TAP_STUB:: MEASURE TCK CYCLE = 10000ps # 023411: cmp_top(reset): Detected reset assertion. Will disable errwarnmon # TAP_STUB:: (2 TCK): TAP_RESET (DONE) # ** Warning: (vsim-3534) [FOFIR] - Failed to open file "tap.cmd" for reading. # Time: 25 ns Iteration: 1 Instance: /cmp_top/tap_stub # TAP_STUB:: (2 TCK, 25000 ps): OPEN tap.cmd fd=0 # TAP_STUB:: (2 TCK, 25000 ps): FAIL TO READ tap.cmd file ERROR # 738411 tso_mon: l2_dir_map_on changed to 0 # 738411 tso_mon: l2_enable changed to 0 # 738411 tso_mon: spc0_dcache_enable changed to 0 # 738411 tso_mon: spc0_icache_enable changed to 0 # 738411 tso_mon: spc0_dc_direct_map changed to 0 # 738411 tso_mon: spc0_lsu_ifu_direct_map_l1 changed to 0 # *Info*: 738411: softint_mon: Thread0 SOFTINT register MATCH: RTL(17'h00000) Vs Expected(17'h00000) # *Info*: 738411: softint_mon: Thread1 SOFTINT register MATCH: RTL(17'h00000) Vs Expected(17'h00000) # *Info*: 738411: softint_mon: Thread2 SOFTINT register MATCH: RTL(17'h00000) Vs Expected(17'h00000) # *Info*: 738411: softint_mon: Thread3 SOFTINT register MATCH: RTL(17'h00000) Vs Expected(17'h00000) # CHECK TIME 738411 #

OpenSPARCを利用する意味

OpenSPARCという商用プロセッサのデータ公開は、当時非常に画期的だったと思うのですが、あまり積極的に活用されていないように感じます。次のような理由が想像できます。

- 通常、OpenSPARCのようなマルチコア/マルチスレッドのプロセッサは何らかのOSを伴って動作する。アプリケーションレベルでプロセッサが何であるかこだわる理由はあまりない。

- ビジネスとして総合的に考えると、ARMやMIPSといった商用コアを利用する方が安い。

また、次のような環境がOpenRISCが公開された2005〜2008年当時と現在では異なります。

- 高機能なプロセッサを内蔵したFPGAが複数のメーカーから安価に提供されている。

- Raspberry Piのように、Linuxが動作するシステムが数千円で販売されている。

では何に役立つのか?

学習用としては、非常に魅力的です。例えば、シミュレーションやFPGAでOpenSPARCを動作させれば、マルチコア、マルチスレッドのプロセッサの内部信号を完全に観測できます。これは、FPGAに搭載させているハードマクロのプロセッサではできないことです。また、カスタムLSIを設計する場合には、低消費電力化のためのクロックゲーティングの手法などは参考になるかも知れません。

OpenSPARCのサイトには、次のような場合に役立つだろうと書かれています。

ソフトウェア開発者:

ハードウェアのソースコードを見ることで、よりハードウェアと統合され、高度に最適化されたアプリケーションを作成することができます。EDA開発者:

あなたのツールの能力をOpenSPARCの商用デザインを使ってテストできます。学界の学生や教授:

OpenSPARCのソースコードを研究したり、またそれを使って独自のソリューションを作成することができます。SolarisやLinux、FreeBSDといったオペレーティングシステムを起動することができるデザインを利用して研究やテストが行えます。

(”About OpenSPARC-What OpenSPARC Means to You”の要約)

まとめ

OpenSPARCの設計データは、プロセッサの学習用として非常に魅力的。

しかし、現在の環境(Linuxなど)で動作させるのはかなり大変。